I.

## American Journal of Engineering Research (AJER) e-ISSN : 2320-0847 p-ISSN : 2320-0936 Volume-03, Issue-04, pp-295-300

www.ajer.org

**Research Paper**

**Open Access**

# **Processor Design Using Square Root Carry Select Adder**

Dhanasekaran. G, Parthasarathy. N, Achuthan. B

Manakula Vinayagar Institute of Technology Manakula Vinayagar Institute of Technology Manakula Vinayagar Institute of Technology

*Abstract:* - http://www.ajer.org/manuscript-submission.html*Index Terms*—Data processing, processors, gate level modification. Delay, power, area, speed.

### INTRODUCTION

The saying goes that if you can count, you can control. Addition is a fundamental operation for any digital system, digital signal processing or control system. A fast and accurate operation of a digital system is greatly influenced by the performance of the resident adders. Adders are also very important component in digital systems because of their extensive use in other basic digital operations such as subtraction, multiplication and division. Hence, improving performance of the digital adder would greatly advance the execution of binary operations inside a circuit compromised of such blocks. The performance of a digital circuit block is gauged by analyzing its power dissipation, layout area and its operating speed.Generally in VLSI techniques we need to satisfy any two of the following criteria such as area, speed and power. The normal adders which we use are satisfying only one trade off but in this SQRT CSLA there is trade off in both area and power. Here we are using 6-Bit BEC(binary to excess-1 converter) to implement the adder element.

### II. LITERATURE SURVEY

In this work we will review the implementation technique of several types of adders and study their characteristics and performance. These are

1. Ripple carry adder, or carry propagate adder,

- 2. Carry look-ahead adder

- 3. Carry skip adder,

- 4. Manchester chain adder,

- **5.** Carry select adders

- 6. Square root Carry select adders

For the same length of binary number, each of the above adders has different performance in terms of Delay, Area, and Power.

**P**arallel adders are digital circuits that compute the addition of variable binary strings of equivalent or different size in parallel.

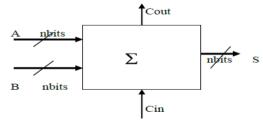

Fig. 1. Block Diagram Of Parallel adders

In ripple carry adders, the carry propagation time is the major speed limiting factorMost other arithmetic operations, e.g. multiplication and division are implemented using several add/subtract steps. Thus, improving the speed of addition will improve the speed of all other arithmetic operations. Accordingly, reducing

www.ajer.org

2014

the carry propagation delay of adders is of great importance. Different logic design approaches have been employed to overcome the carry propagation problem. One widely used approach employs the principle of carry look-ahead solves this problem by calculating the carry signals in advance, based on the input signals. This type of adder circuit is called as carry look-ahead adder (CLA adder).

Fig. 2. Block Diagram Of Carry Look ahead adders

A carry-skip adder consists of a simple ripple carry-adder with a special speed up carry chain called a **skip chain**. This chain defines the distribution of ripple carry blocks, which compose the skip adder.

#### **Carry Skip Mechanics**

The addition of two binary digits at stage i, where i 0, of the ripple carry adder depends on the carry in, Ci, which in reality is the, in order to calculate the sum and the carry out, Ci+1, of stage i, it is imperative that the carry in, Ci, be known in advance. It is interesting to note that in some cases Ci+1 can be calculated without knowledge of Ci.

Fig. 3. Block Diagram Of Carry Skip adders

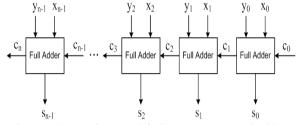

A ripple carry adder allows you to add two k-bit numbers. We use the half adders and full adders and add them a column at a time.Let's put the adder together one step at a time. Arithmetic operations like addition, subtraction, multiplication, division are basic operations to be implemented in digital computers using basic gates like AND, OR, NOR, NAND etc. Among all the arithmetic operations if we can implement addition then it is easy to perform multiplication (by repeated addition), subtraction (by negating one operand) or division (repeated subtraction).Half Adders can be used to add two one bit binary numbers. It is also possible to create a logical circuit using multiple full adders to add N-bit binary numbers.Each full adder inputs a Cin, which is the Cout of the previous adder. This kind of adder is a Ripple Carry Adder, since each carry bit "ripples" to the next full adder.

Fig. 4. Block Diagram Of Ripple Carry adders

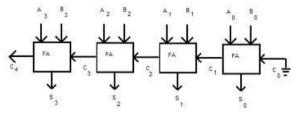

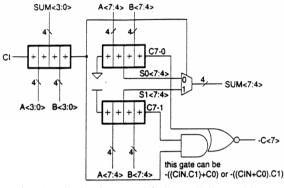

The concept of the carry-select adder is to compute alternative results in parallel and subsequently selecting the correct result with single or multiple stage hierarchical techniques [8]. In order to enhance its speed performance, the carry-select adder increases its area requirements. In carry-select adders both sum and carry bits are calculated for the two alternatives: input carry "0" and "1". Once the carry-in is delivered, the correct

computation is chosen (using a MUX) to produce the desired output. Therefore instead of waiting for the carryin to calculate the sum, the sum is correctly output as soon as the carry-in gets there. The time taken to compute the sum is then avoided which results in a good improvement in speed.

Fig. 5. Block Diagram Of Carry Select adders

The Manchester Carry-Chain Adder is a chain of pass-transistors that are used to implement the carry chain. During precharge, all intermediate nodes (e.g.  $Cout_0$ ) are charged to Vdd. During the evaluation phase, Cout\_k is discharged if there is an incoming carry Cin<sub>0</sub> and the previous propagate signals (P<sub>0</sub>...P<sub>k-1</sub>) are high. Only 4 diffusion capacitances are present at each node, but the distributed RC-nature of the chain results in a delay that is quadratic with the number of bits. Transistor sizing was performed to improve performance. The details are elaborated on in the design strategy section.

#### III. PROPOSED ALGORITHM

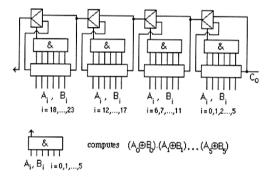

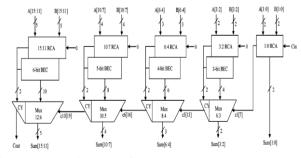

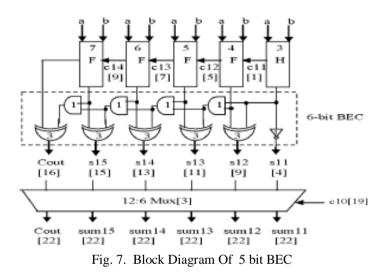

The basic idea of this work is to use Binary to Excess-1 Converter (BEC) instead of RCA with cin=1 in the regular CSLA to achieve lower area and power consumption [2]–[4]. The main advantage of this BEC logic comes from the lesser number of logic gates than the n-bit Full Adder (FA) structure. As stated above the main idea of this work is to use BEC instead of the RCA with Cin=1in order to reduce the area and power consumption of the regular CSLA. To replace the n-bit RCA, an n+1bit BEC is required. A structure and the function table of a 4-b BEC. Fig. 6 illustrates how the basic function of the CSLA is obtained by using the 4-bit BEC together with the mux. One input of the 8:4 mux gets as it input (B3, B2, B1, and B0) and another input of the mux is the BEC output. This produces the two possible partial results in parallel and the mux is used to select either the BEC output or the direct inputs according to the control signal Cin. The importance of the BEC logic stems from the large silicon area reduction when the CSLA with large number of bits are designed. The Boolean expressions of the 4-bit BEC is listed as (note the functional symbols ~NOT, & AND, ^XOR). The Modified CSLA architecture has been developed using Binary to Excess -1 converter (BEC). This paper proposes an efficient method which replaces a BEC using common Boolean logic. The result analysis shows that the proposed architecture achieves the three folded advantages in terms of area, delay and power.

Fig. 6. Block Diagram Of proposed sqrt Carry Select adders

#### IV. 6-BIT BEC

A BEC (binary to excess-1 converter) is a converter which provides the excess 1 value of a corresponding code which is provided at the input.

<u>www.aje</u>r.org

Page 297

| X[3:0]       |                       |

|--------------|-----------------------|

| 0001         |                       |

| 0010         |                       |

|              |                       |

| 1111<br>0000 |                       |

|              | 0001<br>0010<br>11111 |

Table.1. BEC input-output table

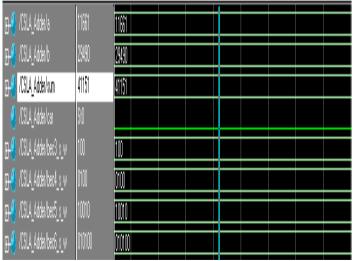

### V. SIMULATION RESULTS

# VI. RTL SCHEMATIC LAYOUT & FLOOR PLAN IN FPGA

VII.

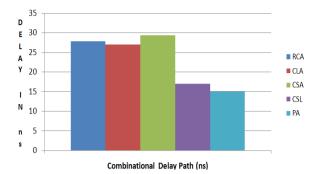

## COMPARISON OF AREA, SPEED AND POWER

| S.No                  | Parameters               | RCA   | CLA   | CSA   | CSL   | PA    |  |  |

|-----------------------|--------------------------|-------|-------|-------|-------|-------|--|--|

| 1                     | 2 Input Xor Gate         | 32    | 32    | -     | •     | •     |  |  |

| 2                     | 3 Input Xor Gate         | •     | -     | 16    | 48    | 41    |  |  |

| AFTER SYNTHESIS       |                          |       |       |       |       |       |  |  |

| 3                     | Number of Slices         | 19    | 18    | 22    | 18    | 25    |  |  |

| 4                     | 4 input LUT              | 33    | 32    | 39    | 32    | 44    |  |  |

| 5                     | Bonded IOB               | 50    | 50    | 50    | 50    | 49    |  |  |

| 6                     | Combinational            | 27.81 | 27.07 | 29.38 | 17.03 | 14.97 |  |  |

| 0                     | Delay Path (ns)          |       |       |       |       |       |  |  |

| AFTER MAPPING         |                          |       |       |       |       |       |  |  |

| 7                     | 4 Input LUT              | 33    | 32    | 39    | 32    | 44    |  |  |

| 8                     | Number of Slices         | 24    | 24    | 25    | 21    | 25    |  |  |

| 9                     | Gate Count               | 198   | 192   | 234   | 192   | 267   |  |  |

| AFTER PLACE AND ROUTE |                          |       |       |       |       |       |  |  |

| 10                    | External IOB             | 50    | 50    | 50    | 50    | 49    |  |  |

| 11                    | Number of Slices         | 24    | 24    | 25    | 21    | 25    |  |  |

| POWER CONSUMPTION     |                          |       |       |       |       |       |  |  |

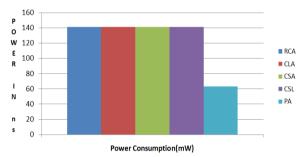

| 12                    | Power<br>Consumption(mW) | 141   | 141   | 141   | 141   | 63    |  |  |

COMBINATIONAL DELAY PATH OF VARIOUS 16-bit ADDERS

POWER CONSUMPTION OF VARIOUS 16-bit ADDERS

### VIII. CONCLUSION

The Proposed adder is very faster when compared to other conventional adders. The proposed adder consumes low power when compared to other conventional adders. Hence a high speed low power adders is proposed. In this proposed adder a set of 20 bits will be evaluated in just 8 clock pulses.

### IX. ACCKNOWLEDGEMENT

The authors are very proud to thank S.Arunmozhi, HOD, ECE department, Manakula Vinayagar Institute Of Technology and V. Rajesh, Assistant Professor, of the department of ECE, Manakula Vinayagar Institute Of Technology for their contribution to this work.

### REFERENCES

- [1] Reduced latency IEEE floating-point standard adder architectures. *Beaumont-Smith, A.; Burgess, N.; Lefrere, S.; Lim, C.C.;* Computer Arithmetic, 1999. Proceedings. 14th IEEE Symposium on ,14-16 April 1999

- [2] M.D. Ercegovac and T. Lang, "Digital Arithmetic." San Francisco: Morgan Daufmann, 2004.

- [3] Using the reverse-carry approach for double datapath floating-point addition.*J.D. Bruguera and T. Lang.* In Proceedings of the 15th IEEE Symposium on Computer Arithmetic, pages 203-10.

2014