| American Journal of Engineering Research (AJER)        | 2016           |  |

|--------------------------------------------------------|----------------|--|

| <b>American Journal of Engineering Research (AJER)</b> |                |  |

| e-ISSN: 2320-0847 p-ISS                                | N:2320-0936    |  |

| Volume-5, Issue                                        | -7, pp-106-111 |  |

|                                                        | www.ajer.org   |  |

| Research Paper                                         | Open Access    |  |

# A Novel High Gain DC-DC Step up Converter

M. Al Mamun<sup>1</sup>, Golam Sarowar<sup>2</sup>, Dr. Md. Ashraful Hoque<sup>3</sup>

<sup>1</sup>(Lecturer, Dept. of EEE, Southeast University, Bangladesh) <sup>2</sup>(Assistant Professor, Dept. of EEE, Islamic University of Technology, Bangladesh) <sup>3</sup>(Professor, Dept. of EEE, Islamic University of Technology, Bangladesh)

**ABSTRACT:** High gain dc-dc converters are widely used to maximize the energy harvest for renewable energy systems, for example, photovoltaic systems and fuel cell. Conventional boost converters usually operates at extreme duty cycle to obtain high voltage gain. Operation at extreme duty cycle leads to reverse recovery problem at the switches, high conduction loss, electromagnetic interference etc. This paper proposes a very high gain dc-dc step up converter operating at very low duty cycle (i.e. duty cycle <0.5). The additional advantage of the proposed converter is that a single control signal is used for the switches which reduces the operation complexity. The steady-state theoretical analysis described in this paper is finally verified by simulation results. **Keywords:** dc-dc boost converter, duty cycle, voltage gain, voltage stress, voltage ripple

### I. INTRODUCTION

In the recent years, the demand of renewable energy systems, for example, photovoltaic systems, fuel cell etc. has increased significantly due to the shortage and environmental threat of fossil fuels. As these renewable systems generate dc power at low voltage level, high gain dc-dc step up converters are getting more and more attentions and lots of researches have been conducted on it [1]. Also, the industrial applications, for example, uninterruptable power supply, high intensity discharge lamps for automobile headlamps, X-ray systems, TV-CRTs require high step-up voltage gain dc-dc power conversion [2]–[4]. To obtain high gain dc-dc conversion several dc-dc converters are employed which are basically divided into two categories-non isolated and isolated converters. Non isolated converters like conventional boost converter, cascaded converter, switched inductor and switched capacitor converters operate at high duty cycle to obtain high voltage gain [5]-[6]. Operating at high duty cycle leads to some unavoidable problems like reverse recovery problem, high conduction loss and electromagnetic interference etc. Self-lift converter, dual and multi-output dc-dc converters discussed in [7]-[9] can almost overcome these problems. These converters can give different dc voltage levels but the voltage gains are not that much high than that of the conventional boost converter.

On the other hand, isolated converters such as fly-back converter, push-pull converter, forward converter, bridge converter etc. involve transformer to isolate the input side from output side. By increasing the turns ratio of the transformer, it is possible to have a high voltage gain. But this also leads to some unavoidable problems, for example, non-linearity of the transformer, voltage spike at the switches during the off state due to the increased inductance, larger size, higher cost etc. [10]-[13].

This paper presents a very high gain non isolated dc-dc step up converter which is able to overcome the above issues. It operates at a very low duty cycle (i.e. duty cycle < 0.5). The switches used in the converter circuit are controlled by a single control signal which reduces the operation complexity and increases the efficiency. The rigorous steady-state analysis is verified by the software PSIM.

Rest of the paper is organized as follows. Operation of the proposed converter with different operating modes and mathematical validation are presented in section II. Section III presents Simulation results and section IV ends the paper with a conclusion.

### II. PROPOSED CONVERTER

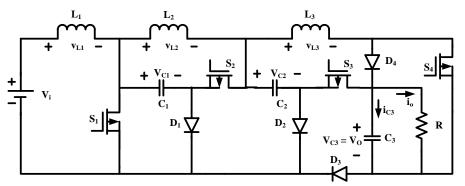

The proposed converter in Fig. 1 involves three inductors ( $L_1$ ,  $L_2$  and  $L_3$ ), three capacitors ( $C_1$ ,  $C_2$  and  $C_3$ ), four diodes ( $D_1$ ,  $D_2$ ,  $D_3$  and  $D_4$ ) and four high frequency controlled switches ( $S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$ ). MOSFETs are used as the high frequency controlled switches and these are operated based on a single duty cycle generated by Pulse Width Modulation (PWM) technique.  $V_i$  represents the low dc input voltage from PV source or fuel cell. The resistive load is connected across the capacitor  $C_3$ .

Fig. 1: Proposed high gain dc-dc step up converter

#### 1. Steady State Analysis of the Proposed Converter

The operation in steady state is discussed as follows.

Let,

$V_i$  = Low input voltage

$V_{LI}$  = Voltage across inductor  $L_I$

$V_{L2}$  = Voltage across inductor  $L_2$

- $V_{L3}$  = Voltage across inductor  $L_3$

- $V_{CI}$  = Voltage across capacitor  $C_I$

$V_{C2}$  = Voltage across capacitor  $C_2$

$V_{C3}$  = Voltage across capacitor  $C_3$

$V_O = V_{C3}$  = Output voltage across R

$T_s$ = Switching time period of controlled switches

$T_{on}$  = Switch ON time period of controlled switches

D =duty cycle of controlled switches (ratio of  $T_{on}$  to  $T_s$ )

#### 1.1. When S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>and S<sub>4</sub>are Turned OFF

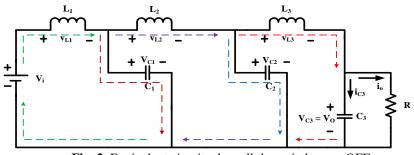

When all four switches are turned OFF, all four diodes  $D_1$ ,  $D_2$ ,  $D_3$  and  $D_4$  are forward biased and this is depicted in Fig. 2.  $V_i$ ,  $L_1$ ,  $L_2$  and  $L_3$  energize  $C_1$ ,  $C_2$ ,  $C_3$  and supply power to the load. KVL applied in the loops in Fig. 2 gives the voltages across  $L_1$ ,  $L_2$  and  $L_3$  as follows,

$$V_{Ll} = V_i - V_{Cl}....(1)$$

$$V_{L2} = V_{Cl} - V_{C2}....(2)$$

$$V_{L3} = V_{C2} - V_{C3}....(3)$$

Fig. 2. Equivalent circuit when all the switches are OFF

### 1.2. When S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>and S<sub>4</sub>are Turned ON

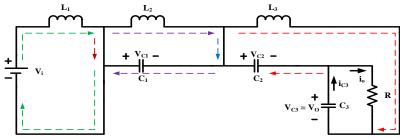

When all four switches are turned ON, all four diodes  $D_1$ ,  $D_2$ ,  $D_3$ ,  $D_4$  are reversed biased and this is depicted in Fig. 3. Now, the inductors  $L_1$ ,  $L_2$  and  $L_3$  are energized by the source voltage  $V_i$  and the capacitors  $C_1$ ,  $C_2$  and  $C_3$ . The load is supplied by the capacitor  $C_3$  and  $V_i$ . KVL applied in the loops in Fig. 3 gives the voltages across  $L_1$ ,  $L_2$  and  $L_3$  as follows,

$V_{L1} = V_i.....(4)$   $V_{L2} = V_{C1}....(5)$  $V_{L3} = V_{C2} + V_{C3}....(6)$

www.ajer.org

Fig. 3. Equivalent circuit when all the switches are ON

Now, by using equations (1) and (4), volt-second balance across  $L_i$  is given by  $V_i DT_s + (V_i - V_{Cl}) (1 - D) T_s = 0$

$$V_i DT_s + (V_i - V_{Cl}) (1 - V_{Cl}) V_{cl} - V_{cl}$$

Or,  $V_{CI} = \frac{v_1}{1-D}$ Similarly, by using equations (2) and (5), volt-second balance across  $L_2$  is given by  $V_{CI}DT_s + (V_{CI} - V_{C2}) (1 - D) T_s = 0$

Or,

$$V_{C2} = \frac{V_{C1}}{1-D} = \frac{V_i}{(1-D)^2}$$

Similarly, by using equations (3) and (6), volt-second balance across  $L_3$  is given by  $(V_{C2} + V_{C3})DT_s + (V_{C2} - V_{C3})(1 - D)T_s = 0$

$$(V_{C2} + V_{C3})DT_s + (V_{C2} - V_{C3}) (1)$$

Or,  $V_{C3} = \frac{V_{C2}}{1-2D} = \frac{V_i}{(1-D)^2 (1-2D)}$

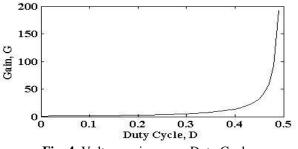

So,  $V_O = \frac{V_i}{(1-D)^2 (1-2D)}$ ....(7) So, voltage gain,  $G = \frac{1}{(1-D)^2 (1-2D)}$

Therefore, from the above equation it is observed that the output voltage is  $\frac{1}{(1-D)^2(1-2D)}$  times the input voltage which is significantly high. It is possible to have a very high voltage gain if the duty cycle D < 0.5. The duty cycle should not be equal to 0.5 as it will cause an infinite voltage gain at the output. If the duty cycle is more than 0.5, then the voltage gain will be negative. The voltage gain *G* with respect to duty cycle *D* is plotted in Fig. 4

Fig. 4. Voltage gain versus Duty Cycle

### **III. SIMULATION RESULTS**

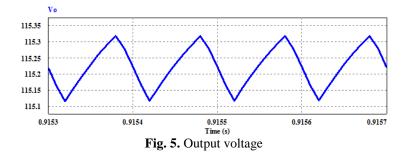

The proposed converter circuit is designed and implemented by using PSIM 9.0. The circuit parameters taken for the simulation are tabulated in Table I. Mathematical calculation of the output voltage  $V_0$  is performed by equation (7) and it is found to be 115.03 V. The simulation gives the value of output voltage very near to 115.03 V with a negligible ripple contentwhich is within prescribed tolerable limit [14] as shown in Fig. 5. The ripple content is controlled by controlling the value of  $C_3$ .

| Parameters                  | Value   |

|-----------------------------|---------|

| Input voltage $(V_i)$       | 12 V    |

| Switching Frequency $(F_s)$ | 10 kHz  |

| Inductor $(L_l)$            | 1 mH    |

| Inductor $(L_2)$            | 3 mH    |

| Inductor $(L_3)$            | 3mH     |

| Capacitor $(C_l)$           | 1000 µF |

| Capacitor ( $C_2$ )         | 1000 µF |

| Capacitor ( $C_3$ )         | 1000 µF |

| Load across $C_3$           | 100 Ω   |

| Duty Cycle (D)              | 0.369   |

Table IParameter Table

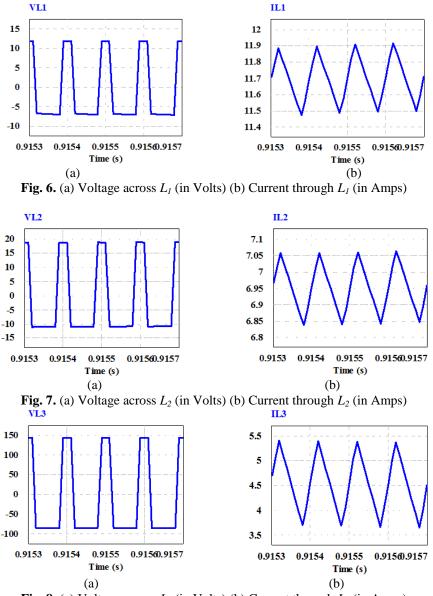

Volt-second balances of  $L_1$ ,  $L_2$  and  $L_3$  are shown in Fig. 6, Fig. 7 and Fig. 8 respectively along with currents through them. The currents are within limit and the ripple contents can be minimized by choosing appropriate values of inductances of  $L_1$ ,  $L_2$  and  $L_3$ .

Fig. 8. (a) Voltage across  $L_3$  (in Volts) (b) Current through  $L_3$  (in Amps)

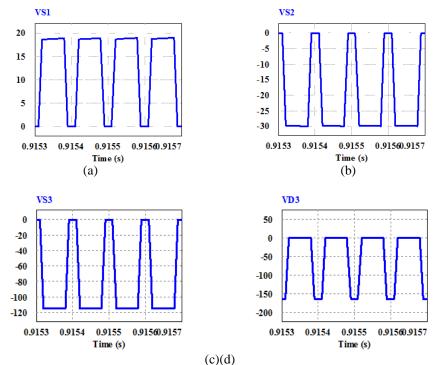

The voltage stress across the power switches and diodes is a crucial parameter. The theory and the simulation shows that the voltage stresses across the switch  $S_1$  and diode  $D_1$  are same as the voltage across  $C_1$ shown in Fig. 9 (a) which is relatively low compared to other switches and diodes. So, the diode and the

www.ajer.org

switch to be used as  $S_1$  and  $D_1$  respectively can be of low voltage rating which reduces the cost and size of the converter. Voltage stresses across the switch  $S_2$  and diode  $D_2$  shown in Fig. 9 (b) are equal to the voltage across  $C_2$  which is higher than the  $S_1$  and  $D_1$ . Therefore, the voltage ratings of  $S_2$  and  $D_2$  should be higher than  $S_1$  and  $D_1$ . Similarly, the voltage stresses across the switches  $S_3$ ,  $S_4$  and diode  $D_4$  shown in Fig. 9 (c) are equal to the voltage across  $C_3$ . As  $V_{C3}$  is the maximum voltage of the converter, voltage ratings of  $S_3$ ,  $S_4$  and  $D_4$  should be high. Voltage stress across  $D_3$  shown in Fig. 9 (d) is equal to the sum of the voltages across  $C_2$  and  $C_3$ . Therefore, the diode to be used as  $D_3$  should be of highest voltage rating. As MOSFETs and IGBTs are popularly used as power electronic switches, the switches used in the proposed converter can be either MOSFETs with the voltage and current ratings of 500 V and 50 A respectively or IGBTs with the voltage and current ratings of 1200 V and 400 A respectively [15]. Since the voltage and current of the proposed converter.

Fig. 9. (a) Voltage stress across  $S_1$  (b) Voltage stress across  $S_2$ (c)Voltage stress across  $S_3$ (d) Voltage stress across  $D_3$

| Parameters Converters                                       | Conventional Step Up<br>Converter     | Proposed Converter                                                           |

|-------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------|

| Voltage gain                                                | $\frac{1}{1-D}$                       | $\frac{1}{(1-D)^2 (1-2D)}$                                                   |

| Range of duty cycle, D                                      | 0 < <i>D</i> < 1                      | 0 < <i>D</i> < 0.5                                                           |

| Output voltage ripple                                       | 0.2939% of average output voltage     | 0.176% of average output voltage                                             |

| Input Inductor current ripple                               | 16.73% of average inductor<br>current | 3.763% of average inductor<br>current                                        |

| Highest voltage stress across the switch(es)                | $\frac{V_i}{1-D}$                     | $\frac{V_i}{(1-D)^2 (1-2D)}$ across $S_4$ and $S_3$                          |

| Highest voltage stress across the diode(s)                  | $\frac{V_i}{1-D}$                     | $\frac{V_i}{(1-D)^2} + \frac{V_i}{(1-D)^2 (1-2D)} \operatorname{across} D_3$ |

| Conduction loss at the switches (proportional to <i>D</i> ) | Higher due to extreme duty cycle      | Lower due to lower duty cycle                                                |

| Table IICompar | ison between C | Conventional Ste | ep Up Converter | and Proposed Converter |

|----------------|----------------|------------------|-----------------|------------------------|

|                |                |                  |                 |                        |

r

2016

2016

The comparison shown in Table II between the conventional step up converter and proposed converter for identical input voltage of 12 V, input inductor of 1 mH and capacitor across the load of 1000  $\mu$ Fmakes the proposed one superior to the conventional one. It is observed that the proposed converter has a higher voltage gain at lower duty cycle than the conventional one. The amount of peak to peakoutput voltage ripple and peak to peak input inductor current ripple in the proposed one is lower. This makes it possible to use the capacitors and inductors of lower value which makes the size of the proposed converter smaller. But the voltage stresses across the switches and the diodes are higher in the proposed converter. As the magnitudes of the voltage stresses are within the prescribed tolerable limit [15], this can be acceptable to obtain high voltage gain. Again, as the conduction loss of a switch is proportional to the duty cycle [15], the proposed converter offers lower conduction loss than that of the conventional one.

### **IV. CONCLUSION**

This paper presents a very high gain dc-dc step up converter which has several advantages over conventional step up converters. The proposed converter gives a very high voltage gain at a low duty cycle (i.e. duty cycle < 0.5) which is not possible by the conventional boost converters. Low duty cycle reduces the reverse recovery problem, conduction loss and electromagnetic interference at the switches. It offers low peak to peak output voltage ripple and low peak to peak input inductor current ripple which makes it possible to use smaller capacitors and inductors. The operation of all the switches is based on a single duty cycle that reduces the controlling complexity of the converter. It can give the same voltage gain without using transformer as that of the isolated converters that reduces the size and cost of the proposed converter. Considering all these advantages, the proposed converter is suitable for high step-up voltage conversion applications and the simulation results verify the correctness.

#### REFERENCES

- [1] W. Li, Y. Zhao, J. Wu, and X. He, "Interleaved high step-up converter with winding-cross-coupled inductors and voltage multiplier cells," *IEEETrans. Ind. Electron.*, vol. 27, no. 1, pp. 133–143, Jan. 2012.

- [2] C. S. Chin, P. Neelakantan, and H. P. Yoong, "Maximum power point tracking for PV array under partially shaded conditions," in *Proc. IEEECICSyN*, 2011, pp. 72–77.

- [3] J. C. Rosas-Caro, J. M. Ramirez, F. Z. Peng, and A. Valderrabano, "A dc-dc multilevel boost converter," *IET-Elect. Power Appl.*, vol. 59, no. 1, pp. 129–137, Jan. 2009.

- [4] W. Li, J. Liu, J. Wu, and X. He, "Design and analysis of isolated ZVTboost converters for highefficiency and high-step-up applications," *IEEETrans. Power Electron.*, vol. 22, no. 6, pp. 2363–2374, Nov. 2007.

- [5] B. Axelrod, Y. Berkovich, and A. Ioinovici, "Transformer less DC-DC converters with a very high DC line-to-load voltage ratio," in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), 2003, pp. III-435-III-438.

- [6] R. J. Wai and R. Y. Duan, "High-efficiency DC/DC converter with high voltage gain," IEE Proc. Electric Power Applications, vol. 152, no. 4, pp. 793-802, Jul. 2005.

- [7] F. L. Luo; X. Chen, "Self-lift DC-DC Converters," Power Electronic Drives and Energy Systems for Industrial Growth, vol. 1, pp. 441-446, Dec. 1998.

- [8] Ray-Lee Lin; Chi-Rung Pan; Kuang-Hua Liu, "Family of single-inductor multi-output DC-DC converters," 2009 International Conference onPower Electronics and Drive Systems (PEDS), pp.1216-1221, 2-5 Nov. 2009.

- [9] Charanasomboon, T.; Devaney, M.J.; Hoft, R.G., "Single switch dual output DC-DC converter performance," IEEE Transactions on Power Electronics, vol.5, no.2, pp.241-245, Apr 1990.

- [10] D. Cao, S. Jiang, and F. Z. Peng, "Low cost transformer isolated boost half-bridge micro-inverter for single-phase grid-connected photovoltaic system," in *Proc. IEEE Appl. Power Electron. Conf.*, 2012, pp. 71–78.

- [11] B. R. Lin and F. Y. Hsie, "Soft-switching zeta-flyback converter with a buck-boost type of active clamp," *IEEE Trans. Ind. Electron.*, vol. 54, no. 5, pp. 2813–2822, Oct. 2007.

- [12] C. M. Wang, "A novel ZCS–PWM flyback converter with a simple ZCS PWM commutation cell," *IEEE Trans. Ind. Electron.*, vol. 55, no. 2, pp. 749–757, Feb. 2008.

- [13] M. Nymand and M. A. E. Alldersen, "High efficiency isolated boost dc/dc converter for high power low voltage fuel-cell applications," *IEEE Trans.Ind. Electron.*, vol. 57, no. 2, pp. 505–514, Feb. 2010.

- [14] Ned Mohan, "Power Electronics: A First Course," John Wiley & Sons, Inc., Wiley, 2012

- [15] Muhammad H. Rashid, "Power Electronics Handbook: Devices, Circuits, And Applications," 3<sup>rd</sup> Edition, Elsevier, 2011

www.ajer.org