| American Journal of Engineering Research (AJER) | 2018           |

|-------------------------------------------------|----------------|

| American Journal of Engineering Res             | earch (AJER)   |

| e-ISSN: 2320-0847 p-ISS                         | N:2320-0936    |

| Volume-7, Iss                                   | ue-9, pp-01-07 |

|                                                 | www.ajer.org   |

| Research Paper                                  | Open Access    |

# Implementation Of Sepic Dc-Dc Voltage Converter Using Voltage Mode And Proportional Integral Controllers.

Nentaweyilwatda Goshwe And Gyang John Dung

Department of Electrical & Electronics Engineering, University of Agriculture, Makurdi, Nigeria Corresponding author: Nentaweyilwatda Goshwe

ABSTRACT: Achieving a regulated DC output from a fluctuating DC source that is efficient and ripple free posed a challenge in power electronic applications. This paper presents a Single-ended Primary Inductor (SEPIC) DC-DC voltage converter which has the advantage of mitigating these challenges by supplying a regulated DC output voltage to a variable-load from a fluctuating DC input voltage with high efficiency. Voltage Mode and Proportional Integral Controllers were applied to the power circuit and the results were compared. The voltage level at the output of the converter is controlled by the duty cycle of the controller using pulse width modulation (PWM). Due to the cyclic switching nature of the Pulse Width Modulation of a SEPIC converter, the converter circuit was modelled using State Space Average (SSA) technique. SEPIC converter is a fourth order system, Pade approximation technique was used to reduce the fourth order model to a linearsecond order model. The linearized model of the SEPIC voltage converter was simulated using MATLAB/SIMULINK. The best tuned values using trial and error method of the rise time, settling time, overshoot, peak value, gain margin and phase margin were achieved at 3.78e-12 secs, 2.86e-11 secs, 20.4%, 1.2, -280dB at 2.92e+04 rad/s and 63.4 degrees at 3.86e+11 rad/s respectively. The output voltage under load condition gives 11.98 V and it is almost ripple free. It shows an estimated percentage error range from 0.17 % to 1.41 %, which is within the design limits. In comparison, the PI controller gives a more efficient output voltage with less ripples and settles faster compared to the VMC.

**Keywords:**DC-DC converter, Proportional-Integral (PI) controller, Voltage Mode Control (VMC), Single Ended Primary Inductor Converter (SEPIC), Continues Conduction Mode (CCM, Pulse Width Modulated (PWM), State Space Average (SSA), Pade approximation technique,trial and error method.

Date of Submission: 25-08-2018

Date of acceptance: 08-09-2018

#### I. INTRODUCTION

The ever increasing reliance on electronic devices that utilize DC power supply with stable output voltage cannot be overemphasized. Voltage regulators have been used to provide such reference voltages but they are not efficient in terms of power lost. Batteries have been used as an option but they lose their energy content rapidly, have limited life cycle and depth of discharge (Venkatanarayanan and Nanthini, 2014). Single-ended primary inductor (SEPIC) DC-DC voltage converter stems these challenges by supplying a regulated DC output voltage to a variable-load resistance from a fluctuating DC input voltage with high efficiency(Kanaanet al., 2009). The essential characteristic of this converter is that the switch is operated only in one of two states; either fully on or fully off (Continuous Conduction Mode (CCM), or Discontinuous Conduction Mode (DCM) unlike other types of electrical circuits where the control elements are operated in a linear active region (Vorperian, 1990, Venkatanarayanan and Saravanan2014).

SEPIC exchanges energy between the capacitors and inductors in order to convert from one voltage level to another and is controlled by the duty cycle of the controller using pulse width modulation (PWM)(Rashid, 2004). Ideally, when a switch is on, it has zero voltage drops and will carry any current imposed on it, but when a switch is off, it blocks the flow of current regardless of the voltage across it (Vadivooet al., 2014 and Paranthagan et al 2015). For this application a switching frequency of 100 KHz is selected as a good compromise between the size of inductors and efficiency.Furthermore, by keeping the signal digital most noise effects are minimized which is a prime benefit of choosing pulse width modulation (PWM) to control the switch(Holmes et al, 2003).Due to the SEPIC converter cyclic switching nature of the PWM, the

converter is modelled using State Space Average (SSA) technique that linearized the non-linear system to a linear system for analysis(Ramasamy and Thangavel, 2012). Pade Approximation method was used to reduce system from fourth order to a linear second order system.

SEPIC converter comes with the advantage of a regulated output that can easily extended to multiple outputs, smaller output voltage ripple, good steady-state performances, excellent transient performance and the same output polarity with input.SEPIC DC-DC converters are commonly used in applications requiring regulated DC power, such as computers, medical instrumentation, communication devices, television receivers, switch mode power supply, solar systems, inverters and battery chargers (Comines and Munro, 2002).

#### II. SEPIC DC-DC VOLTAGE CONVERTER

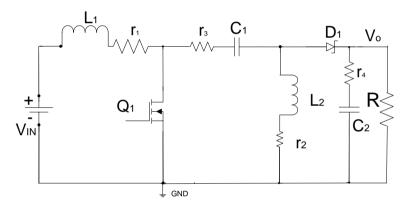

Single-ended Primary Inductance Converter (SEPIC) is a DC-DC voltage converter that will boost, buck or allow the electrical potential (voltage) at its output to be at the desired level with the same polarity as that of the input Figure 1. The term "single ended" means that only one switch (MOSFET) in the converter controls energy exchange between capacitors and inductors. SEPIC DC-DC voltage converter consist of two inductors ( $L_1$  and  $L_2$ ), two capacitors ( $C_1$ , and  $C_2$ ), a diode( $D_1$ ) and switch ( $Q_1$ ). The inductors and capacitors have equivalent series resistances  $r_1$ ,  $r_2$ ,  $r_3$ ,  $r_4$ , respectively. When the pulse is high, the switch is on, inductor  $L_1$  is charged by the input voltage and inductor  $L_2$  is charged by capacitor  $C_1$ . The diode is off and the output is maintained by capacitor  $C_2$ . When the pulse is low, the Switch is off, the inductors output through the diode to the load and the capacitors are charged. During a SEPIC's steady-state operation, the average voltage across capacitor  $C_1$  ( $V_{C1}$ ) is equal to the input voltage ( $V_{in}$ ). Capacitor  $C_1$  blocks direct current (DC), the average current across  $C_1$  ( $I_{C1}$ ) is zero, making inductor  $L_2$  the only source of load current.

Figure 1:SEPIC DC-DC voltage converter schematic circuit diagram.

When  $Q_1$  is turned on, the energy stored in  $L_2$  is transferred to  $C_2$  through  $D_1$  and supplying the energy to Load. Therefore the current across the inductor  $L_1$  and  $L_2$  are

| (1)                              |

|----------------------------------|

| (2)                              |

|                                  |

| (3)                              |

| (4)                              |

|                                  |

| (5)                              |

| uous conduction mode as:         |

| (6)                              |

| e:                               |

|                                  |

|                                  |

| (8)                              |

|                                  |

| = Switch on time, $t_{off} = Sv$ |

|                                  |

Where T = Switching Period,  $f_{SW}$  = Switching Frequency,  $t_{on}$  = Switch on time,  $t_{off}$  = Switch off time and D = Duty cycle.

Page 2

The change in current is estimated at 25% of the input current, therefore the inductor ripple current is  $\Delta I_{L} = I_{in} \times 25\% = \frac{I_{0} \times V_{0} \times 25\%}{V_{in (min)}}$ (9)

With two separate inductors, the inductance is given by:

$$L_1 = L_2 = \frac{V_{\text{in}\,(\text{min}\,)} \times D_{\text{max}}}{\Delta I_L \times f_{\text{sw}}}$$

(10)

If the ripple voltage estimated at 5%, then the capacitor  $C_1$  will be

$$C_1 = \frac{I_0 \times D_{max}}{\Delta V_{C1} \times f_{sw}}$$

(11)

The output Capacitor  $(C_2)$ :

$$C_{2} \geq \frac{I_{0} \times D_{max}}{\Delta V_{ripple} \times f_{sw}}$$

(12)

$C_1 = 450 \ \mu\text{F}, C_2 = 220 \ \mu\text{F}, L_1 = L_2 = 8.16 \ \mu\text{H} \text{ and } P_0 = 120 \ \text{W}$

#### 2.1 Modelling Of The Sepic Converter

The state space equations of the circuit in each of the circuit configurations can be written, when  $Q_1 = 1$ ,  $DT \le t \le T$

$$\begin{aligned} \dot{x} &= A_1 x + B_1 V_{in} \\ D(t) &= 0 \text{ and when } Q_1 &= 0 \\ y &= A_2 x + B_2 \\ Where; \end{aligned} \tag{13}$$

x- Represent electric charge

A - Represent system matrix of the uncontrolled converter (SEPIC)

B - Represent input matrix of the converter

C - Represent output matrix of the converter

D - Represents the direct transmission matrix of the converter

V<sub>in</sub> - Represent control input (U)

y - Represent output voltage (V<sub>o</sub>)

Given the two binary values of the switching function D(t) 1 and 2 can be combined to obtain the nonlinear and time variant state space model of the converter. To produce an average description of the circuit over a switching period using equations 13 and 14, the equations are time weighted and average resulting in equations 14 and 15 over one cycle.

$$\dot{\mathbf{x}} = (\mathbf{A}_1 \mathbf{D} + \mathbf{A}_2 (1 - \mathbf{D}))\mathbf{x} + (\mathbf{B}_1 \mathbf{D} + \mathbf{B}_2 (1 - \mathbf{D}))\mathbf{V}_{in}$$

(15)

$$V_{0} = (C_{1}D + C_{2}(1 - D))x + (E_{1}D + E_{2}(1 - D))V_{in}$$

(16)

Where A<sub>1</sub> and B<sub>1</sub> for switch on, A<sub>2</sub> and B<sub>2</sub> for switch off, D and (1 - D) represent  $t_{on}$  and  $t_{off}$  respectively.

| $\frac{dI_1}{dI_1}$                              |  |  |  |      |

|--------------------------------------------------|--|--|--|------|

| $\frac{1}{dt}$ $I_1$                             |  |  |  |      |

| $dI_2$ $I_2$                                     |  |  |  |      |

| $\dot{\mathbf{x}} = \overline{dt}$ , $x = V_1$ , |  |  |  | (17) |

| $\frac{dV_1}{dt}$ $V_2$                          |  |  |  |      |

| $dV_2$                                           |  |  |  |      |

| dt                                               |  |  |  |      |

Thus, the transfer functions of the output voltage over duty cycle from equations 1 to 4 will be:

$$\frac{V_o(s)}{d(s)} = \frac{A_1 S^4 + A_2 S^3 - A_3 S^2 - A_4 S + A_5}{S^4 + A_6 S^3 - A_7 S^2 - A_8 S - A_9} V_{in}$$

(18)

The above equation is the small signal averaged state space model of the transfer function of output to variation in duty cycle control.Applying Padé approximation on the 4<sup>th</sup> order equation 18 will yield

www.ajer.org

$\frac{V_o(s)}{d(s)} = \frac{B_1 S + B_2}{B_3 S^2 + B_4 S + B_5} V_{in}$ (19)

The plant (SEPIC) DC-DC converter transfer function from equation (18) in terms of VMC:  $\frac{V_0(s)}{V_{in}(s)} = \frac{A_1S^4 + A_2S^3 - A_3S^2 - A_4S + A_5}{S^4 + A_6S^3 - A_7S^2 - A_8S - A_9} \hat{d}(s) = G_s$  (20)

And

The characteristic equation equated to zero from equation 20 above:  $1 + G_c G_s = 0$  (21) Substituting,

$$1 + \frac{A_{1}S^{4} + A_{2}S^{3} - A_{3}S^{2} - A_{4}S + A_{5}}{S^{4} + A_{6}S^{3} - A_{7}S^{2} - A_{8}S - A_{9}} \dot{d}(s) \quad G_{c} = 0$$

$$G_{c} \ge -\frac{S^{4} + A_{6}S^{3} - A_{7}S^{2} - A_{8}S - A_{9}}{(A_{1}S^{4} + A_{2}S^{3} - A_{3}S^{2} - A_{4}S + A_{5})\dot{d}(s)}$$

(22)

G<sub>c</sub>, is the tuning parameters for the trial and error method

#### 2.2.1 Control Methods

If  $G_s$  is the Plant (SEPIC) transfer function and  $G_c$  PI controller in negative feedback mode to the SEPIC (feed forward) system, then

$$Kp + \frac{K_i}{s} = G_c \tag{23}$$

Where Kpis the Proportional term and  $\frac{K_i}{r}$  is the Integral term

The values of the PI controller parameters (Kp and Ki) are selected by using the trial and error method. The PI controller ensures the movement of the process towards the set point and eliminates the residual steady state error. A properly designed PI controller makes the system insensitive to disturbance and change of parameters.

#### **III. RESULTS AND DISCUSSION**

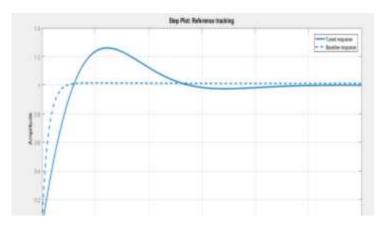

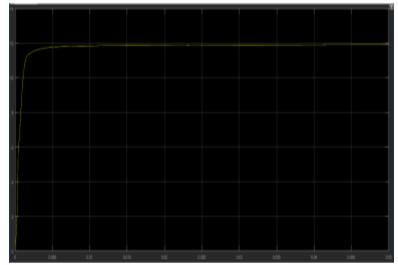

The system was simulated using MATLAB/SIMULINK for easy analysis and the feedback tuned using trial and error method. The trial and error tuning approach of PI controller is based on estimation of the input voltage, the nonlinear disturbances due to changes in circuit parameters, input source and load. This implies that the tuning is repeated a number of times to obtain the best power quality values for the voltage converter. Figure 4 and Table 1 are the results of the trial and error tuning of the rise time, settling time, overshoot, peak value, gain and phase margin of the tuning of the steady state parameters of the PI controller. The best values of the trial and error tuning were achieved rise time of 3.78e-12 secs, settling time 2.86e-11 secs and overshoot of 20.4% and peak value of 1.2, gain margin of -280dB at 2.92e+04 rad/s and phase margin of 63.4 degrees at 3.86e+11 rad/s

Table 1: Corresponding parameters values from PI controller tuning snap shot

|                                                         | Tuned                                                          |

|---------------------------------------------------------|----------------------------------------------------------------|

| Кр                                                      | 0.0016003                                                      |

| Ki                                                      | 2380153478.1603                                                |

| Kd                                                      | 0                                                              |

| Tf                                                      | n/a                                                            |

|                                                         |                                                                |

| Performance and Robustnes                               | 5                                                              |

| Performance and Robustnes                               | s<br>Tuned                                                     |

|                                                         | -                                                              |

| Performance and Robustnes<br>Rise time<br>Settling time | Tuned                                                          |

| Rise time                                               | Tuned<br>3.78e-12 seconds                                      |

| Rise time<br>Settling time                              | Tuned<br>3.78e-12 seconds<br>2.86e-11 seconds                  |

| Rise time<br>Settling time<br>Overshoot                 | Tuned<br>3.78e-12 seconds<br>2.86e-11 seconds<br>20.4 %        |

| Rise time<br>Settling time<br>Overshoot<br>Peak         | Tuned<br>3.78e-12 seconds<br>2.86e-11 seconds<br>20.4 %<br>1.2 |

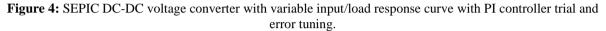

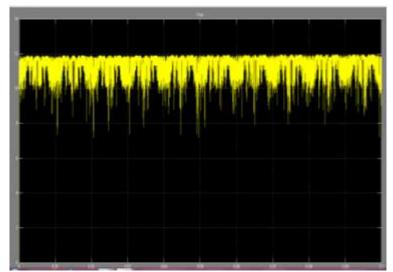

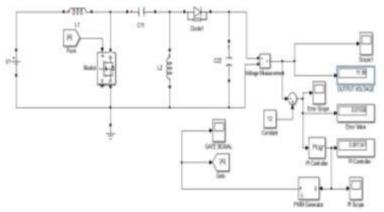

The output of the SEPIC converterusing VMC has a lot of ripples as shown on the graph of the output voltage in Figures 5, 6 and 7. The output voltage was between 7.80 to 11.80 V at minimum input voltage of 6 V and between 11.80 to 16.80 V at maximum input voltage.

Figure 5: SEPIC VMC simulation diagram under load condition.

Figure 6: SEPIC VMC output voltage graph under load condition at maximum input voltage

Figure 7: SEPIC VMC output voltage graph under varying input/load condition.

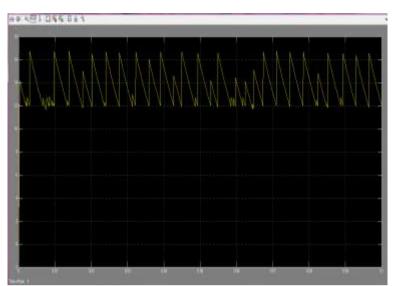

The output voltage SEPIC DC-DC voltage converter using PI controller at minimum and maximum input voltage under no load are as shown on Figures8 and 9. The output voltage under load condition gives 11.98 V and it is almost ripple free. It shows an estimated percentage error range from 0.17 % to 1.41 %, which is within the design limits. In comparison, SEPIC DC-DC voltage converter with PI controller has proven to be more efficient, it has less ripples and settles faster compared to the VMC.

Figure 8: SEPIC converter simulation diagram under no load condition with PI controller

Figure 9: The Graph of the SEPIC on load using PI controller under variable input.

### **IV. CONCLUSION**

This paper has established that SEPIC DC-DC voltage converter with PI controller has proven to be more efficient, it has less ripples and settles faster compared to the VMC. The results from SEPIC output have confirmed the assertion on its excellent filtering properties when reasonable amount of gain is used, hence its preference as converter of choice for DC-DC conversion. The response time and smooth filtering properties of the SEPIC converter equally agree with publications of Zhao and Kaminski, 2009. Furthermore, if the SEPIC DC-DC voltage converter using VMC is use to power any electronic device, the ripples on the power supply will result in overheating.

#### RERENCES

- Comines, P. and Munro, N. (2002). PID controllers: Recent Tuning Methods and Design to Specification. IEE P-Contr. Theory. Ap., 149(1): 46-53.

- [2]. Holmes, D. G. and Lipo, T. A. (2003).Pulse Width Modulation for Power Converters Principles and Practice. Hoboken, NJ: IEEE Press

- [3]. Kanaan, H.Y., K. Al-Haddad, A. Hayek and I. Mougharbel, 2009. Design, study, modelling and control of a new single-phase high power factor rectifier based on the single-ended primary inductance converter and the Sheppard-Taylor topology. IET Power Electron., 2(2): 163-177.

- [4]. Paranthagan,B. Marimuthu, M. and Pramsi Shamili,S. (2015). Comparative Analysis of Performance of the SEPIC Converter Using PID and Fuzzy Logic Controllers for LED Lighting Applications. International Journal of Emerging Technology in Computer Science & Electronics. Vol. 12(2).

- [5]. Rashid, M. H.(2004). Power Electronics: Circuits, Devices, and Applications. 3rd Ed, Pearson/Prentice Hall. (Book)

- [6]. Venkatanarayanan, S. and Nanthini, M. R. M. (2014). Design and Implementation of SEPIC and Boost Converters for Wind and Fuel cell Applications. IEEE International Conference on Innovations in Engineering and Technology (ICIET'14) Volume 3,

- [7]. Venkatanarayanan, S. and Saravanan, M. (2014). Proportional-integral Control for SEPIC Converter. Research Journal of Applied Sciences, Engineering and Technology. Vol. 8(5), page 623-629.

- [8]. Vorperian, V. (1990). Simplified analysis of PWM converters using model of PWM switch, Parts I (CCM) and II (DCM). IEEE Trans. on Aerospace Electronic Systems. Vol. 26, page 497-505

Nentaweyilwatda Goshwe "Implementation Of Sepic Dc-Dc Voltage Converter Using Voltage Mode And Proportional Integral Controllers."American Journal of Engineering Research (AJER), vol. 7, no. 09, 2018, pp. 01-07